# Power amplifier design

#### 3 POWER AMPLIFIER DESIGN

### 3.1 Classes of operation and biasing

#### 3.1.1 Class-A

Class-A operation is characterized by a constant DC collector (or drain) voltage and current. This class of operation is required for linear amplifiers with severe linearity requirements including:

- Drivers in SSB transmitters where a 2-tone 3rd-order intermodulation of at least –40 dB is required

- Drivers in TV transmitters where the contribution to the gain compression must be very low, i.e. not more than a few tenths of a dB

- All stages of TV transposers. These are tested with a 3-tone signal and the 3rd-order intermodulation products must be below –55 to –60 dB. The driver stages should only deliver a small contribution to the overall intermodulation, so they have to operate at even lower efficiency than the final stage (as this is the only way to reduce distortion in class-A).

Though the theoretical maximum efficiency of a class-A amplifier is 50%, because of linearity requirements, the efficiency in the first two applications listed above will be no more than about 25%. And in TV transposers, the efficiency is only about 15% for the final stage and even less for the driver stages.

The transistor power gain in a class-A amplifier is about 3 to 4 dB higher than that of the same transistor operating in class-B. This is because the conduction period of the drain current in class-A is 360° and in class-B only 180° (electrical degrees). Therefore, the effective transconductance in class-B is only half that in class-A.

### 3.1.1.1 DISTORTION

SSB modulation is mainly used in the HF range: 1.5 to 30 MHz. When testing transistors for this application, Philips uses a standard test frequency of 28 MHz. Owing to its variable amplitude, an SSB signal is sensitive to distortion.

# 3.1.1.1.1 2-TONE INTERMODULATION DISTORTION TEST

### 3rd and 5th-order products

This is the most common distortion test. In this test, two equal-amplitude tones 1 kHz apart are applied to the input of the amplifier under test. Practical amplifiers will never be completely linear, and the most important distortion products they produce are the 3rd and 5th order ones, because these are in or very near to the pass-band.

### NOTE TO SECTION 3

For clarity in equations, identifiers such as R1, +jB2, –jX3 in drawings are written as  $R_1$ , +j $B_2$ , –j $X_3$  in the body text.

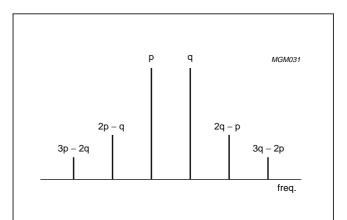

If the frequencies of the two input tones are denoted by p and q, the 3rd-order products are at frequencies of 2p–q and 2q–p, see Fig.3-1. The 5th-order products which usually have smaller amplitudes are at 3p–2q and 3q–2p. Note, the two intermodulation products of the same order don't necessarily have equal amplitudes. This can be due to non-ideal decoupling of the supply voltages, i.e. decoupling that is insufficiently effective at all the frequencies involved. Philips publishes the largest value in data sheets.

Fig.3-1 Position of the main intermodulation distortion products in the 2-tone test where p and g are the input tones.

### Power relationships

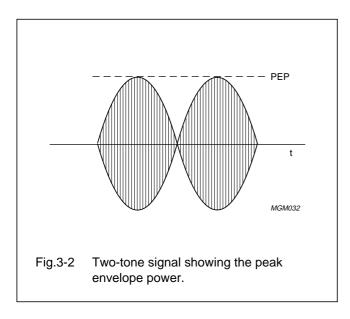

If the tones at p and q are each of 10 W, then the combination has an *average* (*calorific*) power of 20 W. The two tones can however combine in phase or out of phase, producing an RF signal of variable amplitude. When the two tones are in phase, the voltage amplitude is twice that of one tone, so the power is four times that of one tone (in this example: 40 W). This maximum power is called the peak envelope power (PEP) and is commonly published in data sheets. When the two tones are in anti-phase, their combined amplitude is zero. In the ideal case, i.e. with no distortion, the envelope of the combined signal consists of half sine waves, see Fig.3-2.

# Power amplifier design

-8 dB

-16 dB

-16 dB

-16 dB

-7 dB

-7 dB

-16 dB

-7 dB

-7

In class-A applications, distortion products are nearly always specified relative to the amplitude of one of the input test tones. As a general guideline, in the linear region of a class-A amplifier, every 1 dB reduction of output power reduces 3rd-order intermodulation distortion by 2 dB.

# 3.1.1.1.2 3-TONE TEST FOR TV TRANSPOSER APPLICATIONS

In a TV transposer, vision and sound are amplified together, so the distortion requirements are more severe, and it is usual to measure intermodulation using a 3-tone signal. The most popular test (DIN 45004B, para.6.3: 3-tone uses tones of –8 dB, –16 dB and –7 dB with respect to a 0 dB reference power level called the peak sync power. The first tone (–8 dB) represents the vision carrier, the second (–16 dB) a sideband, e.g. the colour carrier, and the third (–7 dB) the sound carrier. This combination of tones has a real peak power which is very close to the 0 dB level, namely: +0.02844 dB or +0.66%.

Another important relationship is the ratio of the average power to the 0 dB level. This ratio is 0.3831, so the 0 dB level is found by multiplying the calorific power by 2.61.

In the 3-tone test, the frequency of the -7~dB tone is 5.5 MHz higher than that of the -8~dB tone, while the frequency of the -16~dB tone is varied between the other two to produce the most intermodulation. If the frequencies of the tones are denoted by p, q and r respectively, we are primarily interested in the 3rd-order intermodulation product p+r-q which is inside the passband and which, in addition, usually has the largest amplitude, see Fig.3-3.

The test requirement for this product for a *complete* transposer is –51 dB with respect to the 0 dB reference level. This implies that the requirements for final stages are more severe (typically –55 dB) while those for driver stages more severe still (typically –60 dB).

In another 3-tone test method, the amplitude of the audio carrier is reduced from -7 dB to -10 dB. This has several effects:

- The actual peak power is only 76.2% of the 0 dB level

- The calorific power is 28.36% of the 0 dB level

- The intermodulation requirements are more severe.

Because one of the tones is reduced by 3 dB, the intermodulation product at f<sub>p+r-q</sub> is also reduced by 3 dB provided the amplifier is operating in the linear region.

# 3.1.1.1.3 RELATIONSHIP BETWEEN 2- AND 3-TONE TEST RESULTS

Theoretically, the first-mentioned 3-tone test and the 2-tone test measurement of SSB amplifiers are related. When (but only when) the PEP of the 2-tone test and the 0 dB level of the 3-tone test are equal, there is always a 13 dB difference in the intermodulation distortion. For example, if, an intermodulation of –40 dB is measured in the 2-tone test, –53 dB will be measured in the 3-tone test. Further, the 2-tone intermodulation should be measured relative to the two equal-amplitude tones and the 3-tone intermodulation relative to the 0 dB level.

Class-A amplifiers for TV transposers and transmitters behave in a similar way to those for SSB driver stages. So, reducing the output power by 1 dB reduces 3rd-order intermodulation by 2 dB.

## Power amplifier design

#### 3.1.1.2 BIASING

For MOS transistors, biasing is very simple. The temperature coefficient of the  $I_D$  versus  $V_{GS}$  curve is almost zero at the optimum operating point so an adjustable resistive divider is sufficient. For bipolar transistors, the situation is more complicated because of the temperature dependency of  $h_{FE}$  and  $V_{BE}$ .

In an audio amplifier, it is usual to stabilize the operating point by means of an emitter resistor and a base potentiometer. In an RF amplifier, however, it is preferable to ground the emitter to obtain maximum power gain as illustrated in Fig.3-4.

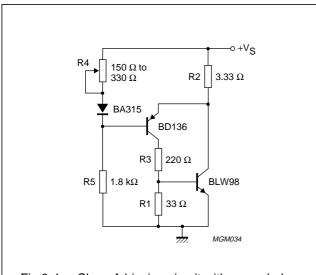

Fig.3-4 Class-A biasing circuit with grounded emitter for maximum power gain.

### 3.1.1.2.1 DESIGN EXAMPLE

In this example, a bias circuit must be designed such that the BLW98 RF transistor operates at  $V_{CE} = 25$  V and  $I_{C} = 850$  mA. The auxiliary transistor is a small PNP audio power transistor: BD136. Owing to the large negative feedback in the final circuit (Fig.3-4), the operating point of the BLW98 is extremely well stabilized for variations in ambient temperature and for the  $h_{FE}$  spread of the BLW98.

For instance, if h<sub>FE</sub> rises due to an increase in ambient temperature, the collector voltage of the BLW98 will fall slightly, causing a decrease in the collector current of the BD136 and therefore in the base current of the BLW98.

The BA315 diode is used to compensate the temperature coefficient of the  $V_{BE}$  of the BD136. The variable resistor in series with this diode serves to adjust the  $I_{C}$  of the BLW98 accurately at the desired value.

#### 3.1.1.2.2 CALCULATION OF COMPONENT VALUES

#### BD136 collector current

The supply voltage is chosen 2 to 3 V higher than the  $V_{CE}$  of the BLW98, e.g. 28 V (to provide sufficient negative feedback). The  $h_{FE}$  of the BLW98 can vary from 15 to about 100. To reduce the  $I_C$  variation of the BD136, the BLW98 is pre-loaded with a resistor between base and emitter ( $R_1$  in Fig.3-4). The  $I_B$  of the BLW98 can vary from 8.5 to 57 mA while the required  $V_{BE}$  for an  $I_C$  of 850 mA is about 0.98 V. If 30 mA flows through  $R_1$ , the required resistance is: 0.98/0.03 ~ 33  $\Omega$ .

The  $I_C$  of the BD136 can now range from 38.5 to 87 mA with an average value of 51 mA. The BD136 has a typical  $h_{FE}$  of 100, so its  $I_B$  is approximately 0.5 mA and its average emitter current is 51.5 mA. The current through the collector resistor,  $R_2$ , of the BLW98 is then: 0.85 + 0.0515 = 0.9015 A. For a voltage drop of 3 V (28 – 25 V), a 3.33  $\Omega$  resistor (3/0.9015) rated at a rather high 2.7 W (3  $\times$  0.9015) is required.

#### Protection resistor

To protect the BLW98 and to reduce the dissipation in the BD136, a resistor,  $R_3$ , is included between the collector of the BD136 and the base of the BLW98. The value of  $R_3$  must be calculated on the basis of the minimum  $h_{FE}$  of the BLW98, and thus on the maximum  $I_C$  of the BD136 of 87 mA. As the  $V_{BE}$  of the BLW98 is about 1 V and the  $V_{CE(sat)}$  of the BD136 is less than 1 V, the maximum voltage drop across  $R_3$  must be less than 23 V. This means a maximum value of:  $23/0.087 = 264\ \Omega$ , say  $220\ \Omega$ , and the maximum dissipation in  $R_3$  is  $0.087^2\times220 = 1.67$  W.

### Base potentiometer

Finally, the BD136 base potentiometer components (R<sub>4</sub>, R<sub>5</sub> and the BA315) have to be determined. The potentiometer current must be high compared with the I<sub>B</sub> of the BD136 (say 10 to 20 I<sub>B</sub>); 13 mA is suitable and corresponds with the test circuit in the data sheet. As the V<sub>BE</sub> of the BD136 is about 0.7 V and the voltage drop across the BA315 diode is 0.8 V, there is a drop of 2.9 V across the variable resistor, so a nominal resistance of 2.9/0.013 = 223  $\Omega$  is required. A range of 150 to 330  $\Omega$  provides sufficient adjustment for practical use. Across resistor R<sub>5</sub>, there is a voltage drop of 24.3 V and a current of 13.5 mA, so a resistance of 24.3/0.0135 = 1.8 k $\Omega$  is required.

Note, unlike some types of bias circuit, this type does not suffer from parasitic oscillations due to high loop gain.

# Power amplifier design

#### 3.1.2 Class-AB

Class-AB operation is characterized by a constant collector voltage and (unlike class-A) a quiescent collector current that increases with drive power. The distortion behaviour is also different to that of class-A. Class-AB operation is used for linear amplifiers with less severe requirements including:

- Final stages of SSB transmitters where a 2-tone

3rd-order intermodulation of about –30 dB is required

- Final stages of TV transmitters where a gain compression of max. 1 dB is required

- Final stages of base stations for cellular radio.

Maximum efficiency is obtained at maximum power, and although the theoretical maximum efficiency of a class-AB amplifier is 78.5%, in practice it is always lower because:

- There are resistive losses both in the transistor and in the output matching circuit

- The collector AC voltage cannot be driven to its maximum value because of distortion requirements

- There is a small quiescent current (for a bipolar transistor, about 2% of the collector current at maximum power and, for a MOSFET, about 12% of the drain current at maximum power).

For HF and VHF amplifiers, in a 2-tone situation, the average efficiency is about 40% which corresponds to an efficiency of 60 to 65% at maximum power (PEP situation). At higher frequencies, the efficiencies are somewhat lower. The power gain of a class-AB amplifier is between those of class-A and class-B amplifiers.

### 3.1.2.1 DISTORTION

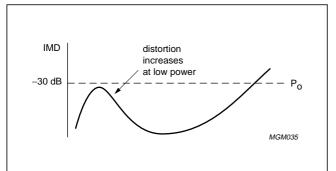

Unlike a class-A amplifier where intermodulation improves as the power is reduced, for a class-AB amplifier, the distortion is as shown in Fig.3-5.

Fig.3-5 Intermodulation distortion as a function of output power for a class-AB amplifier.

The increasing distortion at low powers is due to 'cross-over' distortion, i.e., distortion during the transition from class-A to class-B operation.

#### 3.1.2.1.1 EFFECT OF LOAD IMPEDANCE

An important factor affecting distortion is the load impedance. The optimum value at the fundamental frequency is always specified in Philips' transistor data sheets for the frequency range of interest. The load reactance at the second harmonic is also important. Often, this is solely the output capacitance of the transistor. The collector or drain current contains a substantial second harmonic component which due to the presence of the load reactance causes a second harmonic output voltage component. A relatively small component can be tolerated. However, if it is above say 10% of the voltage at the fundamental frequency, the amplifier will saturate at a lower power than intended, so the allowable distortion is reached at lower power.

This can be solved by adding an external capacitor between collector (or drain) and earth. Though this will reduce gain and efficiency somewhat, it will reduce intermodulation significantly. A good practical rule is that the reactance of the parallel combination of internal and external capacitance at the second harmonic should be about 2.2 times the load resistance at the fundamental frequency. For wideband amplifiers, there is another solution which can be found in application reports, e.g. "NCO8703".

### 3.1.2.2 BIASING

For MOS transistors, biasing is rather easy. In most cases, a resistive voltage divider is sufficient. If necessary, a diode or an NTC thermistor can be included in the lower branch to compensate for the negative t.c. of the gate voltage.

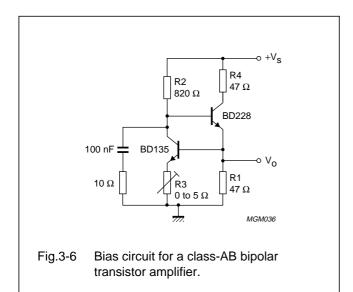

For bipolar transistors, a more sophisticated circuit is required. The circuit has to deliver a constant voltage of about 0.7 V (adjustable over a restricted range) and should have very low internal resistance. The latter is required to accommodate a wide range of 'load' currents (i.e. base drive currents for the RF transistor), whilst maintaining a nearly constant output voltage. Other desired properties are temperature compensation and the lowest possible current consumption. Figure 3-6 shows a circuit meeting these requirements.

The bias circuit has large negative feedback. If the load current increases, the output voltage drops slightly, decreasing the collector current of the BD135 whose collector voltage increases to counteract the drop in output voltage.

# Power amplifier design

#### 3.1.2.2.1 DESIGN EXAMPLE

Calculation of component values

BD228 BASE AND COLLECTOR CURRENT

In this example, it is assumed that the bias circuit is for an amplifier delivering an output power of 100 W at a supply voltage of 28 V. So, if the minimum amplifier efficiency is 50%, the required DC input power is 200 W, corresponding to a collector current of 7.14 A. If the transistors used have a minimum  $h_{FE}$  of 15, the maximum base current can be 0.48 A. Such an amplifier could be the final stage of an SSB transmitter where the output power and therefore also the base current vary from almost zero to 0.48 A. In the bias circuit, a pre-loading resistor,  $R_1$ , is used to reduce the base current variations. To draw 15 mA at 0.7 V,  $R_1$  must be 0.7/0.015 = 47  $\Omega$ . The maximum emitter current of the BD228 will then be nearly 0.5 A. From the published  $h_{FE}$  data for this type, the base current is 15 mA maximum.

The current through the collector resistor,  $R_2$ , of the BD135 is chosen to be twice this value, i.e. 30 mA, to restrict the variations in the collector current of the BD135. The  $V_{BE}$  of the BD228 is about 0.8 V, so the voltage across  $R_2$  is 26.5 V, giving a value of: 26.5/0.03 = 883  $\Omega$  (nearest preferred value: 820  $\Omega$ , 1 W.)

#### **OUTPUT VOLTAGE**

At first sight, the choice of a BD135 in this circuit seems a bit overspecified for a transistor that has to draw only 30 mA. Yet this has been done deliberately because then the  $V_{BE}$  required by the BD135 is low (smaller than the bias voltage to be delivered to the RF amplifier.) The difference

is corrected by the variable resistor,  $R_3$ , in the emitter of the BD135. The output voltage of the bias circuit, and thus the quiescent current of the RF amplifier, can now be adjusted. With a resistor of 5  $\Omega$  max., the output voltage can be adjusted by at least 100 mV, sufficient for this application.

#### PROTECTION RESISTOR

To protect the BD228 against the consequences of a short-circuit of the output voltage, it is advisable to include a resistor,  $R_4$ , in the collector lead. As the BD228 has a  $V_{CE(sat)}$  of 0.8 V max., a voltage drop of 26.5 V across  $R_4$  is allowed at the maximum collector current of 0.5 A. The maximum value of this resistor is therefore 26.5/0.5 = 53  $\Omega$  (nearest preferred value: 47  $\Omega$ .) Note that  $R_4$  must be rated at 12 W ( $I^2R=0.5^2\times47=11.75$ ).

#### **PERFORMANCE**

The internal resistance of this bias circuit is exceptionally small. Values of less than 0.1  $\Omega$  have been measured, so the output voltage varies by less than 50 mV from zero to full load. The value of the output voltage is mainly determined by the V<sub>BE</sub> of the BD135, which has a well-known temperature dependence (about -2 mV/°C), providing reasonable matching with the required V<sub>BE</sub> of RF transistors without any special measures.

This type of bias circuit can develop parasitic oscillations near 1 MHz with highly capacitive loads (such as the supply decoupling capacitors in the RF circuit). This can be prevented by an RC combination between the collector of the BD135 and ground. Good values are 10  $\Omega$  and 100 nF.

#### 3.1.3 Class-B

This class of operation can be used for all RF power amplifiers without linearity requirements, e.g. in portable and mobile radios, base stations (except those for the 900 MHz band) and FM broadcast transmitters.

For bipolar transistors, no biasing is required, i.e.  $V_{BE}=0$ , while MOSFETS are used with very small quiescent drain current, say 2 to 3% of the current at full power. This can be provided in the same way as for class-AB amplifiers.

The collector (or drain) efficiency is about 70% at VHF, while the power gain depends on the frequency of operation.

### 3.1.4 Class-C

This class of operation is *not recommended for bipolar transistors*, because it shortens transistor life, see also Section 2.1.1: V<sub>EBO</sub> rating. An exception can be made for

# Power amplifier design

a very small negative bias (<100 mV) which can be generated with a small resistor between base and emitter.

MOSFETS are more tolerant in this respect and can be adjusted at  $V_{GS} = 0$ , causing only a few dB reduction of power gain. This is not a problem in most cases because the gain is rather high. The main advantage is a higher drain efficiency. A good example is the BLF278 which at 108 MHz in class-B gives 70% efficiency at 22 dB gain, and in class-C, 80% efficiency at 18 dB gain.

#### 3.1.5 Class-E

This class of operation is discussed in more detail in application report "COE82101". With an optimum choice of component values for the output matching network of the transistor, collector or drain efficiencies of 85% can be reached. However, the use of class-E is restricted as beyond 60 to 70 MHz, efficiency falls significantly.

### 3.1.6 Influence of driver stages on intermodulation

Most linear amplifiers (i.e. class-A and class-AB) consist of a cascade of two or more amplifier stages. The overall distortion is mainly caused by the final stage because the driver stages are generally designed to have a lower distortion. In fact, attention to the design of the driver stage will pay dividends in overall performance as the following analysis illustrates.

The total distortion of a multi-stage amplifier, d<sub>tot</sub>, can be determined from:

$$d_{tot} = 20 log \left( 10^{d_1/20} + 10^{d_2/20} + .... \right)$$

where  $d_1$ ,  $d_2$  etc. are the intermodulation products of each stage in dB.

With two stages, e.g. driver plus a final stage, it is useful to know by how many dB the overall distortion worsens for a given difference in distortion between driver and final stage (assuming the driver distortion is the smaller). This relationship is described by:

$$B = 20 \log \left( 1 + 10^{-A/20} \right)$$

where:

A is the absolute difference in distortion between driver and final stage, and

B is the increase in distortion in the output of the amplifier.

This relationship is summarized in Table 3-1 for a few values. Clearly, if a large increase in distortion is unacceptable, the driver stage has to be substantially better than the final stage.

**Table 3-1** Effect of driver distortion upon overall distortion

| Α                                                              | В                                   |

|----------------------------------------------------------------|-------------------------------------|

| Amount by which driver IMD is superior to final stage IMD (dB) | Increase in IMD of output amp. (dB) |

| 0                                                              | 6.0                                 |

| 5                                                              | 3.9                                 |

| 10                                                             | 2.4                                 |

| 15                                                             | 1.4                                 |

| 20                                                             | 0.8                                 |

### 3.2 Matching

### 3.2.1 Narrow-band (test) circuits

### NARROW-BAND MATCHING CIRCUITS

- Section 3.2.1.1: describes the principles of impedance matching

- Section 3.2.1.2: describes two types of adjustable network, and how to handle high power levels

- Section 3.2.1.3: deals with UHF versions of the networks of the previous section using striplines

- Section 3.2.1.4: discusses the double networks required for very-low transistor impedances

- Section 3.2.1.5: is on π-networks where the trimmers are grounded on one side to avoid 'hand effects'. VHF and UHF versions are given as well as the modifications for low-impedance transistors.

### 3.2.1.1 GENERAL REQUIREMENTS

Every transistor amplifier needs to be impedance matched both at its input and output. In test circuits, the 50  $\Omega$  signal source must be matched to the complex input impedance of the transistor. At the output, the reverse is needed, namely, the 50  $\Omega$  load resistance must be transformed to the optimum complex load impedance of the transistor.

In multistage amplifiers, networks are required in addition, to provide direct matching between two complex impedances. The most important requirement for all matching networks is that power losses must be minimized. In addition, especially for output networks, the

# Power amplifier design

voltage and current loading of the components must be taken into account.

Most matching networks have to be tunable, ideally with a large tuning range and with smooth, continuous control. Unfortunately, these are conflicting requirements so a compromise must be made.

In general, there are no severe requirements on the bandwidth of a matching network. However, it can be advantageous not to make this bandwidth too small, thereby improving the smoothness of the alignment and reducing losses.

The objective of matching is to maximize power transfer. This requires that the source and load impedances are complex conjugates, i.e. they have equal resistance components, and equal reactance components but of opposite sign.

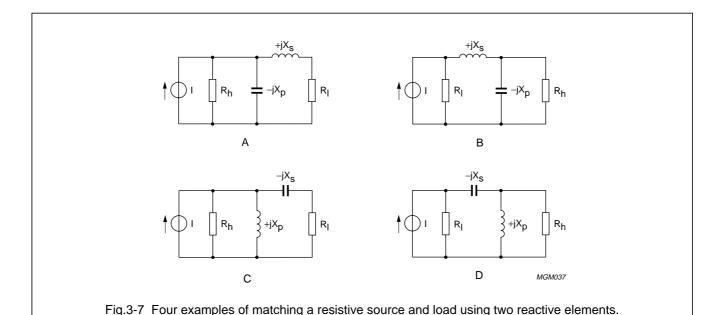

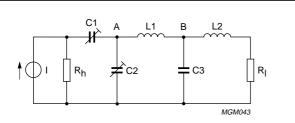

The simplest form of matching between a source with a real (i.e. resistive) internal impedance and a different load resistance can be made using two reactive elements, see Fig.3-7.

In Fig.3-7, A and B have low-pass characteristics and are most commonly used because of their suppression of harmonic components. C and D have high-pass characteristics and, although used less frequently, have advantages in specific cases such as interstage networks.

The higher resistance is denoted by  $R_h$  and the lower by  $R_l$ .  $R_h$  always has a parallel reactance  $(X_p)$  and  $R_l$  a series one with opposite sign  $(X_s)$ .

The component values can be easily calculated from:

$$\frac{X_S}{R_I} = Q = \frac{R_h}{X_p} \tag{1}$$

and

$$\frac{R_h}{R_l} = Q^2 + 1 \tag{2}$$

where Q is the *loaded* Q-factor which has to be small compared with the *unloaded* Q-factor of the components.

**Note:** Equations (1) and (2) are used on many occasions in subsequent sections to determine component values in networks.

Up to now, we have only considered matching two different value *resistances*. In practice, at least one of the impedances is complex, and in such cases, one of the reactances, namely the one closest to the complex impedance, has to be modified.

Suppose that in Fig.3-7, circuit A is used for the input matching of a transistor. If the transistor's input impedance is capacitive,  $X_s$  has to be increased by the absolute value of the transistor's input reactance as Fig.3-8 shows. If the input impedance is inductive, the reverse is needed:  $X_s$  has to be reduced by this amount. Note, if in the latter case the input reactance of the transistor is higher than the calculated  $X_s$ , the new  $X_s$  becomes negative, meaning a capacitor has to be used instead of an inductor.

Similar considerations hold for the other configurations.

# Power amplifier design

Fig.3-8 Adding a series inductance to the input matching circuit A of Fig.3-7 to compensate for the capacitive part of a transistor's input impedance.

#### 3.2.1.2 ADJUSTABLE L AND T NETWORKS<sup>(1)</sup>

Owing to their limited control options, the networks described in the previous section are not really suitable for use in test circuits. This limitation can be overcome in two ways by simple circuit modifications.

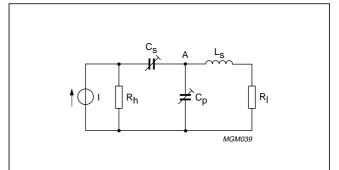

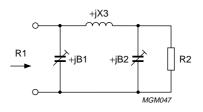

#### 3.2.1.2.1 NETWORK 1

Starting from circuits A (high-to-low transformation) and B (low-to-high transformation) of Fig.3-7,  $X_p$  is made (partly) variable by using a trimmer (optionally with a fixed capacitor in parallel to lower the trimmer current and for smoother control). In addition, a variable capacitor is connected in series with  $X_s$  such that the combination remains inductive. ( $C_s$  can again be the parallel combination of a trimmer and a fixed capacitor). This means the inductance has to be increased to keep the combination's reactance at the calculated value of  $X_s$ , see Fig.3-9.

For the modified network, the new Q-factor for  $L_s$  is

$$Q' = \frac{\omega L_s}{R_l}$$

And since  $L_s$  has increased, Q' is higher than the Q defined in the previous section, meaning the circuit losses are higher and the bandwidth is lower. Therefore, these effects must be reduced as much as possible by restricting the increase in  $L_s$ .

Fig.3-9 Adjustable matching network (based on circuit A of Fig.3-7) suitable for test circuits. A similar network can be made based on circuit B of Fig.3-7.

#### 3.2.1.2.2 NETWORK 2

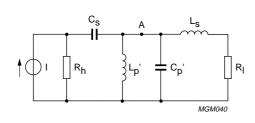

A variant of network 1 is shown in Fig.3-10. This circuit uses smaller capacitances than the circuit of Fig.3-9. And though the harmonic suppression is worse, this can usually be tolerated in input networks.

The calculation of component values is done in two stages. To assist understanding, it is best to imagine this circuit as two cascaded sections (D plus A from Fig.3-7), see Fig.3-11. The first section transforms  $R_h$  to a higher value at point A, and the second transforms this value down to  $R_{\rm l}.$  To restrict the losses and reduction of bandwidth, it is advisable to choose the equivalent parallel resistance at point A no higher than necessary. When making the calculation, note that the combined reactance of  $L_p{}^{\prime}$  and  $C_p{}^{\prime}$  is always negative ( $C_p{}^{\prime}$  dominates), so the combination can be realized by a (variable) capacitor.

Fig.3-10 Variant of the matching network shown in Fig.3-9.

<sup>(1)</sup> Note: Many of the networks in Section 3.2 are 'reversible'.

# Power amplifier design

Fig.3-11 The matching network of Fig.3-10 represented as two cascaded sections to simplify calculation.

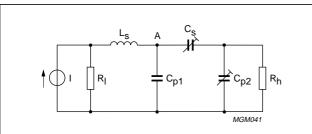

Another possibility is a combination of networks 1 and 2. This is sometimes used in output networks that must handle relatively high power, see Fig.3-12.

The purpose of  $C_{p1}$  is to drain some, say half, of the RF current to ground so that the current through  $C_s$  and  $C_{p2}$  becomes proportionally smaller, allowing components of a lower rating to be used.

The equivalent parallel resistance at point A should be 2 to 3 times  $R_h$  which determines the value of  $L_s$  (from equations (1) and (2), the resistance ratio determines the Q, and  $X_s = QR_l$ ). Next, choose a value for  $C_{p1}$  that is about half that required to transform  $R_l$  to the resistance at point A.

Looking from point A to the left (but including  $C_{p1}$ ), we see an inductive impedance: R+jX, where  $R>R_l$ . The remaining part of the calculation is then the same as for network 1.

Fig.3-12 Matching network formed by combining those shown in Figs.3-9 and 3-10.

With these and the following networks, it is often needed to transform an impedance from series to parallel components or vice versa. For such transformations, the equations given in the previous section for calculating L-networks can be used with  $R_{\rm l}$  as the series resistance component and  $R_{h}$  as the parallel resistance component.

#### 3.2.1.3 UHF NETWORKS

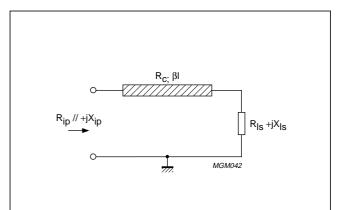

Above 300 MHz, it is not very practical to work with coils, so transmission lines in the form of striplines are preferred, see Fig.3-13. As well as having series inductance, striplines have parallel capacitance which transforms the real part of the load impedance, calling for a modified calculation.

Figure 3-13 is very similar to the right-hand part of the circuit shown in Fig.3-10. The (low) load impedance is known, but note that its imaginary part can be positive or negative depending on the transistor. And  $R_{ip}$  is chosen in the same manner as the resistance at point A in network 2, Section 3.2.1.2.

Next, choose the characteristic resistance of the stripline to satisfy the condition:

$$R_c > \sqrt{R_{ls}R_{ip}}$$

The exact value of  $R_{\text{c}}$  is set by practical considerations as both very narrow and very broad striplines are undesirable.

Fig.3-13 Representation of a stripline used in UHF matching networks.

Power amplifier design

It's now possible to calculate the electrical length ( $\beta$ I) and the parallel input reactance ( $X_{ip}$ ) from the following two equations:

$$\tan \beta I = \frac{-b + \sqrt{b^2 - 4ac}}{2a}$$

where:

$$a = R_c^2 - R_{ls}R_{in}$$

$$b = 2R_c X_{ls}$$

$$c = R_{ls}^2 + X_{ls}^2 - R_{ls}R_{ip}$$

and:

$$X_{ip} = \frac{R_{ls}R_{ip}}{X_{ls} + tan \beta I \left(R_c - \frac{R_{ls}R_{ip}}{R_c}\right)}$$

The values of the (variable) capacitors are calculated as described in Section 3.2.1.2.

#### 3.2.1.4 DOUBLE NETWORKS

In some cases, the input and/or load impedance of the transistor is so low that a direct transformation, as just described in Section 3.2.1.3, leads to very high values of the loaded Q-factor with all its negative consequences. It is then better to add an extra (fixed) section as shown in Figs 3-14 and 3-15.

Fig.3-14 Adding a fixed section to the network of Fig.3-10 avoids high loaded Q-factors.

Fig.3-15 Circuit with the fixed section added to the alternative network of Fig.3-9.

Suppose that  $R_h=50~\Omega$  and  $R_l=1~\Omega.$  A suitable value for the equivalent parallel resistance at point A is then 100 to 150  $\Omega$  (i.e. more than 50  $\Omega$ , but not so big in view of circuit losses and bandwidth). At point B, a value which is the geometric mean of that at point A (say 125  $\Omega$ ) and  $R_l$  is required, namely  $\sqrt{(125\times1)}=11.2~\Omega.$

Without the double network, the loaded Q is:

$$\sqrt{(125-1)} = 11.1$$

and with the double network, it is:

$\sqrt{(11.2-1)}$  = 3.2 which is a significant improvement.

This double network variant also has advantages for output networks. Furthermore, by replacing some or all of the coils by striplines, it can be used at higher frequencies.

#### 3.2.1.5 PI-NETWORKS

#### 3.2.1.5.1 FOR THE VHF RANGE

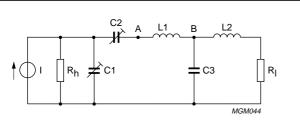

The networks considered up to now have used both parallel and series capacitors. This can be undesirable because of the so-called 'hand-effect' (the influence of an operator's capacitance) when adjusting a variable capacitor with an RF signal on both sides of it. This effect is present even when an insulated adjuster is used. An alternative method of impedance matching which uses only parallel capacitors overcomes this problem, see Fig.3-16.

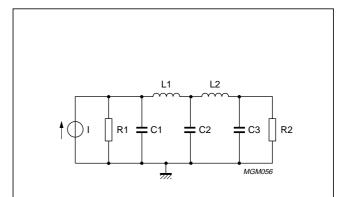

If  $R_l$  is the low transistor output impedance and  $R_h$  the 50  $\Omega$  load resistance, then we start by transforming  $R_l$  up to about 50  $\Omega$  by the fixed section  $L_1$ - $C_1$ . This fixed section is followed by a Pi-network  $C_2$ - $L_2$ - $C_3$  which can transform the impedance either up or down as required, and the Pi-network component values are calculated as follows (see Fig.3-17).

Fig.3-16 Impedance matching circuit using only parallel capacitors.

This arrangement in which only one side of the capacitor is 'hot' allows manual tuning on the grounded side of the capacitor, avoiding the 'hand-effect'.

# Power amplifier design

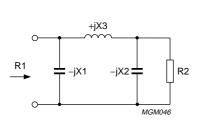

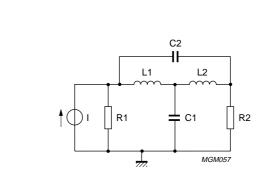

Fig.3-17 Pi-network circuit for the calculation when both  $R_1$  and  $R_2$  have fixed values.

Fig.3-18 Pi-network circuit for the calculation with adjustable input resistance,  $R_1$ .  $R_2$  is fixed, e.g. 50  $\Omega$ .

For the condition:  $X_3 \le \sqrt{R_1 R_2}$ ,

$$X_1 = \frac{R_1 X_3}{R_1 + \sqrt{R_1 R_2 - X_3^2}}$$

and

$$X_2 = \frac{R_2 X_3}{R_2 + \sqrt{R_1 R_2 - X_3^2}}$$

In most cases however, we want to adjust the input resistance by varying  $X_1$  and  $X_2$ , for example, to suit different transistors and for maximum power transfer. Figure 3-18 shows a suitable network in which, for mathematical convenience, susceptances (B =  $\omega$ C) have been used instead of reactances.

The value required for  $X_3$  is determined by the minimum value of  $R_1$ :

$$X_3 = \sqrt{R_{1 \, min} R_2}$$

$$B_{1 \, min} = B_{2 \, min} = \frac{1}{X_3}$$

$$\Delta B_1 = \frac{1}{2R_{1,min}}$$

and

$$\Delta B_2 = \frac{\sqrt{\frac{R_{1 \text{ max}}}{R_{1 \text{ min}}} - 1}}{R_2}$$

So both capacitors have the same minimum value but generally a different control range ( $\Delta$ ).

The losses in this type of Pi-network are in general somewhat higher than those in the networks discussed earlier. The losses increase as the difference between  $\mathsf{R}_1$  (avg.) and  $\mathsf{R}_2$  increases and as the control range increases since in both cases the loaded Q of the components increases.

The losses can be kept within reasonable limits if the average value of  $R_1$  is within a factor of 2 (up or down) of  $R_2$  (i.e.  $R_2/2 < R_1 < 2R_2$ ). For the control range of  $R_1$ , a factor of 4 (total) is generally suitable, providing a control factor of 2 (up and down) from the nominal value.

### 3.2.1.5.2 FOR THE UHF RANGE

The network just described can also be made in a stripline version, see Fig.3-19.

The characteristic resistance of the stripline must satisfy the condition:

$$R_C > \sqrt{R_{1 \text{ min}} R_2}$$

Then the other quantities become:

$$tan \ \beta I = \frac{1}{\sqrt{\frac{{R_c}^2}{{R_{1 \ min}R_2}} - 1}}$$

$$B_{1 \text{ min}} = B_{2 \text{ min}} = \frac{1}{R_{c} \tan \beta I}$$

$$\Delta B_1 = \frac{1}{2R_{1 \text{ min}}}$$

$$\Delta B_2 = \frac{\sqrt{\frac{R_{1 \text{ max}}}{R_{1 \text{ min}}} - 1}}{R_2}$$

# Power amplifier design

So clearly this stripline network has much in common with the previous one.

# 3.2.1.5.3 PI-NETWORK MODIFICATIONS FOR LOW-IMPEDANCE TRANSISTORS

If the transistor impedance is very low (say <5  $\Omega$ ) as occurs in high power situations, there are two options:

- 1. Make the average value of  $R_1$  lower than  $R_2$ , e.g. half of  $R_2$

- Use two pre-matching sections instead of one. If this is done, make the impedance between the two sections equal to the geometric mean of the transistor impedance and the average input resistance of the Pi-network.

#### 3.2.2 Wideband circuits

# WIDEBAND HF MATCHING CIRCUITS OVERVIEW

HF range (Section 3.2.2.1)

- Describes the procedures for input/output matching of MOS and bipolar transistors. Most attention is paid to MOS devices as they are usually the preferred choice for HF applications.

- Section 3.2.2.1.1 describes some output compensation circuits. Output compensation aims to maintain the ideal load impedance over the frequency band of interest to obtain the highest efficiency and lowest distortion. This section explains:

- \* How to compensate a transistor's output capacitance with one or two elements - the latter giving superior results

- \* How to compensate parallel inductances such as RF chokes and/or transformer inductance to improve performance at the lower end of the band, and the selection of compensation (coupling) capacitor(s).

- Section 3.2.2.1.2 deals with the design of input networks to obtain low input VSWR, and high, flat power gain over the whole frequency band.

# $R_{c;\beta}$ $B_{c;\beta}$ $B_{c$

Fig.3-19 Stripline version of the Pi-network of Fig.3-18.

#### 3.2.2.1 THE HF RANGE

This frequency range covers 1.6 to 28 MHz. Most transmitters in this range work with single sideband modulation and wideband power amplifiers. The impedance transformation in these amplifiers can be done either by transmission line type transformers or by compensated conventional transformers (extensively described in application reports "ECO6907" and "ECO7213").

In addition, a number of compensation techniques can be used at both output and input. For the former, this is done to obtain maximum output power and efficiency over the whole frequency band; for the latter, it's done to obtain maximum and flat power gain and good impedance matching over the band.

### 3.2.2.1.1 COMPENSATION AT THE OUTPUT

Compensation of output capacitance

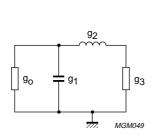

Take as an example the BLF177 MOS transistor. From the published data sheet, this has an output capacitance of 190 pF which rises at full power by about 15% to 220 pF. The capacitor reactance at 28 MHz is about four times the load resistance of 6.25  $\Omega$ . Without compensation, the output VSWR is 1.28 which is rather high. To reduce this VSWR, one or two external components can be used. Compensation with one element is shown in Fig.3-20. Two elements will of course give a better result than one, and is described later.

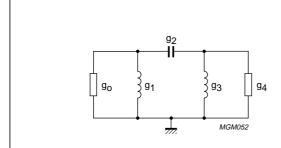

These compensation examples make use of Chebyshev filter theory where it is usual to express the values of the filter elements normalized to a characteristic resistance (source and/or load resistance) of 1  $\Omega$  and to a cut-off (angular) frequency,  $\omega$ , of 1 rad/s. For a low-pass filter, 1 rad/s is the maximum angular frequency, and for a high-pass filter the minimum. Normalized quantities are denoted by  $q_k$  where k is a filter-element identifier (Ref.1).

# Power amplifier design

Single-element compensation

Fig.3-20 Output capacitance compensation using one element.

go: optimum load resistance;

g<sub>1</sub>: output capacitance of device.

In the circuit of Fig.3-20, the filter elements are:

g<sub>0</sub>: the optimum load resistance (known);

g<sub>1</sub>: the output capacitance of the device (known);

g<sub>3</sub>: the real load resistance, and

g<sub>2</sub>: the compensating element inductance.

In normalized form, we can express these quantities as:

$$g_1 = \frac{\sqrt{2}}{\gamma}$$

$$g_2 = \frac{\sqrt{2}\gamma}{1+\gamma^2}$$

$$g_3 = \frac{g_0 \gamma^2}{1 + \gamma^2}$$

where  $\gamma$  is an intermediate quantity (mathematically related to the maximum VSWR in the pass-band) used to simplify the calculations.

From the above, it follows that:

$$g_2 = \frac{2g_1}{g_1^2 + 2}$$

In general,  $g_1 \ll 1$ , so  $\gamma \gg 1$  and as a result,  $g_3 \sim g_0$ .

(De)normalization can be done using:

$$g_0 = R$$

$$g_1 = \omega CR$$

$$g_2 = \omega L/R$$

where:  $\omega$  is the *maximum* angular frequency, and the maximum VSWR is  $g_0/g_3$ .

In the example with the BLF177:

$$g_1 = 1/4$$

$g_2 = 0.2424$  (normalized value), so L = 8.61 nH.

Therefore, the VSWR is 1.031 - a substantial improvement. And though not necessary in this case, it can be made better still as required in driver stages for which compensation with two elements, see Fig.3-21, is preferred.

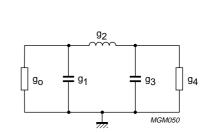

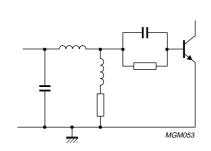

Two-element compensation

Fig.3-21 Output capacitance compensation using two elements.

The calculation is similar to that just described, so in normalized form:

$$g_0 = g_4$$

$$g_1 = g_3 = \frac{1}{\gamma}$$

$$g_2 = \frac{2\gamma}{\gamma^2 + \frac{3}{4}}$$

From this, it follows that:

$$g_2 = \frac{8g_1}{3g_1^2 + 4}$$

Normalization and denormalization is done using:

# Power amplifier design

$g_0 = g_4 = R$

$g_1 = g_3 = \omega CR$

$g_2 = \omega L/R$

where  $\omega$  is again the *maximum* angular frequency.

The maximum VSWR is calculated as follows. For the calculation, it is necessary to introduce a term k where:

$$k = \gamma + \sqrt{(\gamma^2 + 1)}$$

Then:

$$VSWR = \left(\frac{k^3 + 1}{k^3 - 1}\right)^2$$

In the example with the BLF177:

$g_1 = 1/4$

$\gamma = 4$

$g_2 = 0.4776$  (so L = 17 nH)

Therefore, the VSWR = 1.007.

This is principally the same as the HF compensation of a conventional transformer. The only difference is that in the latter case the stray inductance is known and the compensation capacitors have to be calculated.

Compensation of parallel inductances

COMPENSATING ONE PARALLEL INDUCTANCE

It is also worthwhile compensating for the parallel inductances of the RF choke and output transformer found in most amplifiers as their reactances at 1.6 MHz are often about four times the load resistance. In most cases, compensation is provided by the coupling capacitor(s).

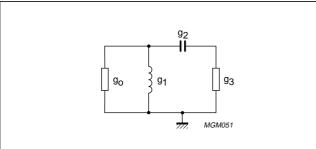

There are also simpler situations where either the RF choke or the impedance transformer is missing. We will start with this case and the equivalent circuit is given in Fig.3-22.

Fig.3-22 Compensation of an RF choke.

This circuit looks much the same as the HF compensation scheme, with the L and the C interchanged.

Mathematically, there is also much in common - only the normalized values have to be inverted. So, for the reactive elements:

$$g_1 = \frac{\gamma}{\sqrt{2}}$$

$$g_2^{} \,=\, \frac{1+\gamma^2}{\sqrt{2}\gamma}$$

$$g_3 = \frac{g_0 \gamma^2}{1 + \gamma^2}$$

From these, it follows that:

$$g_2 = \frac{1 + 2g_1^2}{2g_1}$$

In general,  $g_1$  and  $\gamma$  are >>1, so  $g_3 \sim g_0$ .

Normalization and denormalization are done using:

$g_0 = R$

$g_1 = \omega L/R$

$g_2 = \omega CR$

where  $\omega$  is the *minimum* angular frequency, and the maximum VSWR is again  $g_0/g_3$ .

#### **COMPENSATING TWO PARALLEL INDUCTANCES**

If we have to compensate two parallel inductances of approximately equal value, the equivalent circuit is as shown in Fig.3-23.

Inverting the normalized values for the reactive elements gives:

$g_0 = g_4$

$g_1 = g_3 = \gamma$

$$g_2 = \frac{\gamma^2 + \frac{3}{4}}{2\gamma}$$

From these, it follows that:

$$g_2 = \frac{4g_1^2 + 3}{8g_1}$$

# Power amplifier design

Fig.3-23 Compensation of an RF choke and impedance transformer.

Normalization and denormalization is done using:

$$g_0 = g_4 = R$$

$$g_1 = g_3 = \omega L/R$$

$$g_2 = \omega CR$$

where  $\omega$  is the *minimum* angular frequency and the maximum VSWR is determined in the same way as in the HF situation. So, if  $k = \gamma + \sqrt{(\gamma^2 + 1)}$  as defined earlier:

$$VSWR = \left(\frac{k^3 + 1}{k^3 - 1}\right)^2$$

In the example with a BLF177:

$$g_1 = 4$$

$$\gamma = 4$$

$$g_2 = 2.094$$

Therefore, the VSWR = 1.007

For R = 6.25  $\Omega$  and f = 1.6 MHz, we get C = 33 nF.

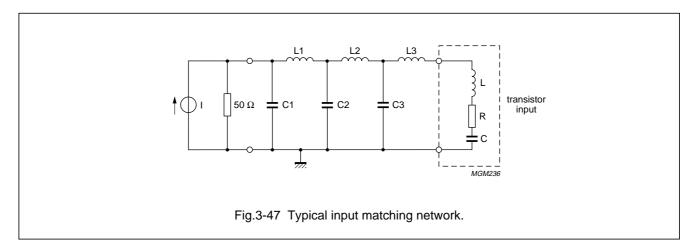

### 3.2.2.1.2 COMPENSATION AT THE INPUT

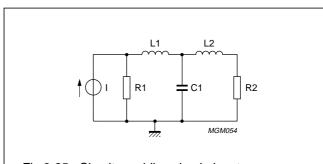

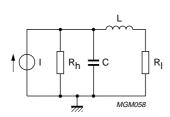

For bipolar transistors, the variations in power gain and input impedance can be compensated with an R-L-C network as decribed in application report "AN98030", and shown in Fig.3-24. The network was designed using a circuit analysis program with an optimization facility.

For MOS transistors, the behaviour of the input impedance is quite different. The main problem here is providing a constant voltage across a rather high input capacitance (for the BLF177: about 745 pF) over the frequency range. At the same time, we want good matching at the input *and* the highest power gain.

Fig.3-24 Compensation circuit of a bipolar transistor input. An example is given in report "AN98030".

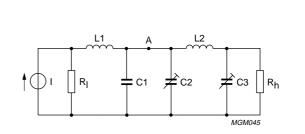

Simply connecting a resistor across the transistor input does not produce good results. Better solutions, the simplest of which is described here (see Fig.3-25), are required. The more advanced ones will be discussed later where their superior performance is really needed.

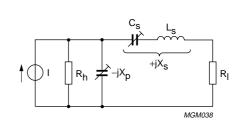

Fig.3-25 Circuit providing simple input compensation of a MOS transistor.

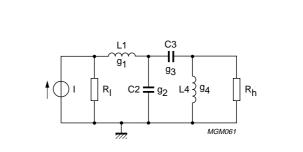

In Fig.3-25, the (transformed) driving generator is represented by the combination I-R<sub>1</sub>, and the input capacitance of the transistor by C<sub>1</sub>. The compensation components are: L<sub>1</sub>, L<sub>2</sub> and R<sub>2</sub>. R<sub>2</sub> should approximately equal R<sub>1</sub>. In addition, the voltage across C<sub>1</sub> should not differ much from that across R<sub>1</sub>. As the required voltage across C<sub>1</sub> is a given quantity, we shall design a circuit with the highest possible value of R<sub>1</sub> to obtain the lowest possible drive power.

Computer optimization programs can be used to investigate what happens when the product  $R_1C_1$  is increased. The aims of optimization are to:

- Minimize the input VSWR over the frequency band, and

- Minimize the variation of the voltage across C<sub>1</sub> over the same band.

# Power amplifier design

Table 3-2 gives the normalized results from such a program.

**Table 3-2** Effect of varying  $\omega C_1 R_1$  in the compensation circuit of Fig.3-25

| $ωC_1R_1$ | $\omega L_1/R_1$ | $\omega L_2/R_1$ | R <sub>2</sub> /R <sub>1</sub> | VSWR <sub>max</sub> | ∆G(dB) |

|-----------|------------------|------------------|--------------------------------|---------------------|--------|

| 0.8       | 0.437            | 0.305            | 0.961                          | 1.21                | 0.19   |

| 1.0       | 0.515            | 0.388            | 0.939                          | 1.34                | 0.31   |

| 1.2       | 0.571            | 0.473            | 0.908                          | 1.51                | 0.44   |

| 1.4       | 0.619            | 0.568            | 0.867                          | 1.74                | 0.64   |

$\omega$  is the maximum angular frequency, and  $\Delta G$  the maximum deviation from the average gain.

From Table 3-2, clearly, a good practical choice is  $\omega C_1 R_1 = 1.0$ . For the BLF177, this means that  $R_1$  can be 7.6  $\Omega$  maximum. For ease of transformation, we chose 6.25  $\Omega$ .

The input impedance of the transistor is not of course a pure capacitance. It also has some series resistance and inductance, so reoptimization is necessary to take account of the real input impedance and power gain of the transistor as a function of frequency.

For driver stages operating at a low power level, negative feedback is sometimes used: an emitter resistor and a collector-base resistor for bipolar devices (with in some cases an inductance in series with the latter to reduce feedback at the high end of the frequency band).

Similarly, for MOS transistors, a resistor is connected between drain and gate. A resistor is not required in the source lead however. The advantage of this feedback method is lower intermodulation distortion. The feedback must not be too large however as such a resistor consumes part (albeit a small part) of the output power.

Fig.3-26 Equivalent circuit of output compensation for the lower VHF range.

#### 3.2.2.2 THE LOWER VHF RANGE

# WIDEBAND VHF MATCHING CIRCUITS OVERVIEW

Lower VHF range (Section 3.2.2.2)

- Though the same circuit configurations used for HF can be used in this range, the higher maximum frequency requires modified component values.

- Section 3.2.2.2.1 describes two circuits that compensate for output capacitance.

- Section 3.2.2.2.2 describes two input networks using more compensation elements than the HF version for higher power gain.

Upper VHF range (Section 3.2.2.3)

- Describes impedance matching (input and output) for this range using low-pass L-sections, with an optional high-pass section.

- Section 3.2.2.3.1 describes a single low-pass section, sufficient for low impedance ratios and/or moderate bandwidths. To meet more stringent requirements, two or three sections are required. Section 3.2.2.3.2 outlines several approaches, some suitable for interstage networks.

- Finally, the effect of non-ideal network components is discussed.

Some military communications transmitters operate in this range. The lowest frequencies used are 25 to 30 MHz and the highest 90 to 110 MHz.

Power amplifiers for this range are similar to those for the HF range. However, impedance matching can only be done with transmission line transformers as described in application report "ECO7703". In addition, more complex methods are required for RF compensation at both output and input.

### 3.2.2.2.1 COMPENSATION AT THE OUTPUT

The output compensation systems described in Section 3.2.2.1.1 provide adequate results in the HF range. For the lower VHF range, somewhat better results can be obtained simply by modifying the component values. The equivalent circuit is shown in Fig.3-26.

First, let  $R_1 = R_2$ ;  $C_2$  does not however have to equal  $C_1$ . Computer optimization for lower VHF yields the results shown in Table 3-3.

# Power amplifier design

The practical limit of usefulness is at  $\omega C_1 R_1 = 1.0$ . If we use this condition with the Chebyshev system described earlier, then the maximum VSWR would be 1.33 instead of 1.29.

**Table 3-3** Computer optimization results of the compensation circuit of Fig.3-26 for the lower VHF range

| ωC <sub>1</sub> R <sub>1</sub> | ωC <sub>2</sub> R <sub>1</sub> | ωL <sub>1</sub> /R <sub>1</sub> | VSWR <sub>max</sub> |

|--------------------------------|--------------------------------|---------------------------------|---------------------|

| 0.6                            | 0.549                          | 0.914                           | 1.08                |

| 0.8                            | 0.693                          | 1.04                            | 1.17                |

| 1.0                            | 0.827                          | 1.10                            | 1.29                |

| 1.2                            | 0.965                          | 1.12                            | 1.44                |

$\omega$  is the maximum angular frequency.  $R_1 = R_2$ .

With this compensation, we can go one step further by dropping the requirement that  $R_2$  has to equal  $R_1$ . Doing this and optimizing again yields the results shown in Table 3-4.

As Table 3-4 shows, for  $\omega C_1 R_1 = 1.0$ , the maximum VSWR is improved to 1.25, and the corresponding value of  $R_2$  is now smaller than  $R_1$ . Whether this is an advantage or not is difficult to say as it is dependent on the desired combination of supply voltage and output power as well as on the possible transformer ratios.

**Table 3-4** Computer optimization results of the compensation circuit of Fig.3-26 for the lower VHF range.  $R_1 \neq R_2$

| $ωC_1R_1$ | $ωC_2R_1$ | ωL <sub>1</sub> /R <sub>1</sub> | R <sub>2</sub> /R <sub>1</sub> | VSWR <sub>max</sub> |

|-----------|-----------|---------------------------------|--------------------------------|---------------------|

| 0.6       | 0.468     | 0.818                           | 0.939                          | 1.08                |

| 0.8       | 0.615     | 0.922                           | 0.897                          | 1.16                |

| 1.0       | 0.738     | 0.943                           | 0.838                          | 1.25                |

| 1.2       | 0.886     | 0.943                           | 0.783                          | 1.36                |

$\omega$  is the maximum angular frequency, and  $R_1 \neq R_2$ .

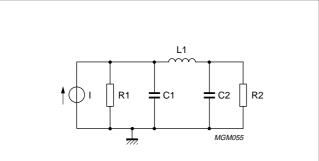

### 3.2.2.2.2 INPUT NETWORKS

For bipolar transistors, it should be possible to use the same type of compensation network used for the HF range in the lower VHF range. However, we shall restrict our considerations to input networks for use with MOS devices.

The problem is the same as for the HF range (maintaining a constant voltage across a capacitance over a wide frequency range, see Section 3.2.2.1.2), but with a substantially higher maximum frequency. So, a more efficient compensation network is needed, requiring more

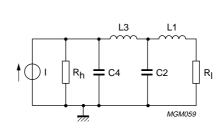

components. The first of two examples is shown in Fig.3-27.

C<sub>2</sub> represents the input capacitance of the transistor. The results obtained by computer optimization are shown in Table 3-5.

Compared with the network described earlier (Fig.3-25 and Table 3-2), there is substantial improvement because  $\omega R_1 C_2$  can certainly be increased up to 1.6, compared with 1.0 for the simpler network, providing higher gain for a given bandwidth.

A second circuit configuration producing as good or even superior results is shown in Fig.3-28. Here, the input capacitance of the transistor is represented by  $C_1$ . Computer optimization yields the results summarized in Table 3-6.

Fig.3-27 Example of an improved compensation circuit for the lower VHF range.

Fig.3-28 Second example of an improved compensation circuit for the lower VHF range.

# Power amplifier design

Table 3-5 Computer optimization results of the compensation circuit of Fig.3-27

| ωR <sub>1</sub> C <sub>2</sub> | $\omega R_1 C_1$ | $\omega R_1 C_3$ | $\omega L_1/R_1$ | $\omega L_2/R_1$ | R <sub>2</sub> /R <sub>1</sub> | VSWR <sub>max</sub> | $\Delta G$ (dB) |

|--------------------------------|------------------|------------------|------------------|------------------|--------------------------------|---------------------|-----------------|

| 1.0                            | 0.460            | 0.501            | 0.870            | 0.836            | 1.02                           | 1.10                | 0.10            |

| 1.2                            | 0.602            | 0.496            | 1.02             | 0.836            | 1.00                           | 1.14                | 0.15            |

| 1.4                            | 0.751            | 0.485            | 1.11             | 0.836            | 0.977                          | 1.21                | 0.20            |

| 1.6                            | 0.887            | 0.476            | 1.15             | 0.845            | 0.955                          | 1.31                | 0.28            |

| 1.8                            | 0.993            | 0.482            | 1.15             | 0.870            | 0.934                          | 1.42                | 0.38            |

$\omega$  is the maximum angular frequency and  $\Delta G$  the maximum deviation from the average gain.

Table 3-6 Computer optimization results of the compensation circuit of Fig.3-28

| 0.5              | 0.0       | 1 /D             | 1 /D             | D /D      | VOMB         | + O ( ID)       |  |

|------------------|-----------|------------------|------------------|-----------|--------------|-----------------|--|

| $\omega C_1 R_1$ | $ωC_2R_1$ | $\omega L_1/R_1$ | $\omega L_2/R_1$ | $R_2/R_1$ | $VSWR_{max}$ | $\Delta G$ (dB) |  |

| 1.0              | 0.591     | 0.392            | 0.336            | 0.977     | 1.12         | 0.11            |  |

| 1.2              | 0.597     | 0.447            | 0.396            | 0.972     | 1.15         | 0.13            |  |

| 1.4              | 0.604     | 0.504            | 0.462            | 0.966     | 1.19         | 0.16            |  |

| 1.6              | 0.584     | 0.584            | 0.536            | 0.961     | 1.21         | 0.18            |  |

| 1.8              | 0.584     | 0.662            | 0.611            | 0.955     | 1.23         | 0.20            |  |

| 2.0              | 0.574     | 0.794            | 0.733            | 0.934     | 1.21         | 0.36            |  |

$\omega$  is the maximum angular frequency and  $\Delta G$  the maximum deviation from the average gain.

Comparing these results with those of the previous case, we see that the product  $\omega C_1 R_1$  can be increased to 1.8 and possibly to 2.0. So, this configuration, even though it uses one component fewer, is better. Experience shows that circuits using inductive coupling between  $L_1$  and  $L_2$  do not improve the VSWR and gain variation performance.

As mentioned earlier, the input impedance of a MOS transistor can be represented by a capacitance, inductance and resistance in series. At high power levels in particular, the resistance cannot be neglected.

As a guideline, reoptimization is necessary when the values of input VSWR and gain variation are inferior to those in Tables 3-2, 3-5 and 3-6.

#### 3.2.2.3 THE UPPER VHF RANGE

To get an idea of the impedance levels in this frequency range, consider a BLF225 MOS transistor able to deliver 30 W at 175 MHz from a 12.5 V supply voltage (Note, bipolar devices for the same range have similar impedance levels).

Suppose that the BLF225 is used in a mobile radio transmitter for the range 132 to 174 MHz. The optimum load impedance is about 2.5  $\Omega$  with a rather small reactive component. At the transistor input, there is an effective capacitance of 215 pF in series with a resistance of 3.2  $\Omega$  and a small inductance of 0.21 nH.

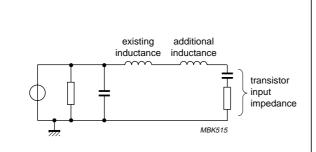

In the literature, most networks for wideband impedance matching are based on pure resistances. So, we have to start by making the impedance at the input approximately real. In theory, this can be done with either a parallel or a series inductance. Though the former should be preferable as it provides a higher impedance, unfortunately, a small inductance in parallel with the input of a transistor can cause large parasitic oscillations. Therefore, we have to use a series inductance, giving a tuned circuit with a loaded Q-factor of 1.53 in the middle of the frequency band. The relative width of this band  $(\Delta f/f_0)$  is 27 to 28% . If the product of loaded Q-factor and relative bandwidth is much less than 1, as in this case, the matching will not be affected significantly.

The remaining task is to match resistances of 3.2  $\Omega$  and 2.5  $\Omega$  to a 50  $\Omega$  source and load over the range 132 to 174 MHz. The most popular type of network for this purpose comes from G.L. Matthaei (Ref.2) where the matching is obtained from one or more low-pass L-sections (the more sections, the lower the VSWR in the pass-band).

The essence of this method is that there are several frequencies in the pass-band at which exact matching occurs. The number of exact matches is equal to the number of sections.

# Power amplifier design

Fig.3-29 Single-section matching network for the upper VHF range.

### 3.2.2.3.1 SINGLE-SECTION MATCHING

First consider when there is just one section, Fig.3-29.  $R_h$  is the higher of the two resistances and  $R_l$  the lower. Exact matching takes place at:

$$f_0 = \sqrt{\frac{1}{2} \left( f_l^2 + f_h^2 \right)}$$

where  $f_l$  is the lower limit of the band and  $f_h$  the upper one.

L and C can be calculated in the same way as described in Section 3.2.1.1. The maximum VSWR in the pass-band follows from the input impedance at one of the band limits.

The results of the calculation for the output, where 2.5  $\Omega$  must be matched to 50  $\Omega$ , are:

$f_0 = 154.4 \text{ MHz}$

L = 11.23 nH

C = 89.84 pF

VSWR = 2.974.

The VSWR calculation is rather complex and is best done using a circuit analysis program. The high VSWR obtained here indicates that one section is not sufficient. Therefore, we shall now consider some possibilities with two sections.

#### 3.2.2.3.2 TWO-SECTION MATCHING

Two low-pass sections

If both sections are low-pass, the situation is as shown in Fig.3-30.

Exact matching takes place at  $f_1$  and  $f_2$  ( $f_2 > f_1$ ) and:

$$f_1 = \frac{1}{2} \sqrt{(2 + \sqrt{2}) f_1^2 + (2 - \sqrt{2}) f_h^2}$$

and

$$f_2 \, = \, \frac{1}{2} \sqrt{\left(2 - \sqrt{2}\right) \, f_1^{\, 2} + \, \left(2 + \sqrt{2}\right) \, f_h^{\, \, 2}}$$

Fig.3-30 Two-section matching network for the upper VHF range.

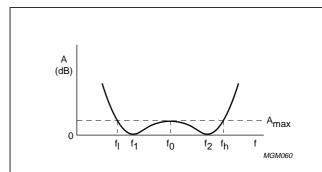

Fig.3-31 Pass-band characteristic of the two-section matching circuit of Fig.3-30.

There is maximum attenuation at the band limits, but also

$$f_0 = \sqrt{\frac{1}{2} \left( f_1^2 + f_h^2 \right)}$$

The pass-band characteristic is shown in Fig.3-31.

To determine the values of the components, we need to define an auxiliary quantity M where:

$$M = L_1 C_2 = \frac{\sqrt{1 - \frac{R_h}{R_l}}}{\omega_1 \omega_2}$$

in which  $\omega_1 = 2\pi f_1$ and  $\omega_2 = 2\pi f_2$ .

Then, for the circuit of Fig.3-30:

$$L_1 \ = \ \sqrt{\frac{-p}{2} + \sqrt{\frac{p^2}{4} - q}}$$

21

# Power amplifier design

where:

$$p = -R_1 \{MR_h(\omega_1^2M - 2) + (R_h - R_l)/\omega_1^2\},$$

and

$$q = -M^2R_1^3R_h$$

And, for the other components:

$$C_2 = M/L_1$$

$$L_3 = C_2 R_1 R_h$$

$$C_4 = L_1/(R_1R_h)$$

.

To calculate the maximum VSWR in the pass-band, the procedure used for single-section matching must again be followed.

For this example, where we need to match from 2.5 to 50  $\Omega$  in the frequency range 132 to 174 MHz, we obtain:

$f_1 = 138.9 \text{ MHz}$

$$C_2 = 197.4 \text{ pF}$$

$f_2 = 168.5 \text{ MHz}$

$$L_3 = 24.67 \text{ nH}$$

$L_1 = 5.343 \text{ nH}$

$$C_4 = 42.74 \text{ pF}$$

The maximum VSWR (from the circuit analysis program) in the pass-band is now 1.173, which is a far better result than with one section (2.974).

Though the calculation procedure described above is rather complicated, direct use of the Matthaei method (Ref.2) is not simple either because:

- Interpolation is required both for impedance ratio and relative bandwidth

- Denormalization must be used, and

- Insertion loss must be converted to VSWR.

One low-pass and one high-pass section

Another method of wideband impedance matching is described by U. Fleischmann. (Refs 3, 4 and 5). In this method, two L-sections are used: one low-pass, the other high-pass. Both sequences are possible, and the resulting pass-band characteristic is almost equal to that of the previous case with two sections. To simplify calculation, we need to define several quantities:

$$f_0 = \sqrt{f_1 f_h}$$

where  $f_l$  and  $f_h$  are the lower and upper limits of the frequency band respectively.

$$d = \frac{f_h - f_l}{f_o}$$

$$m = \frac{R_h}{R_I}$$

$$\epsilon \,=\, \frac{-d^2\sqrt{m}}{4} + \sqrt{\left(\frac{d^2\sqrt{m}}{4}\right)^2 + \left(\frac{d^2+2}{2}\right)}\,\text{, and}$$

$k = \varepsilon \sqrt{m}$ .

Now we are able to calculate the normalized component values, first for when the low-pass section is adjacent to the lower resistance, R<sub>I</sub>, see Fig.3-32.

LOW-PASS SECTION NEAR RI

In this case:

$$g_1 = \frac{1}{k} \sqrt{\frac{k-1}{m}}$$

$$g_2 = \sqrt{m(k-1)}$$

$$g_3 = \sqrt{\frac{m}{k-1}}$$

$$g_4 = \frac{k}{\sqrt{m(k-1)}}$$

Denormalization can be done for each element using:

$$g = \omega_0 L/R_h$$

and

$$g = \omega_0 CR_h$$

where  $\omega_0 = 2\pi f_0$

Then, the maximum VSWR in the pass-band becomes:

$$VSWR = 1/\epsilon^2$$

Fig.3-32 Two-section matching network using two L-sections.

Fig.3-33 Two-section matching network using two L-sections (section sequence reversed compared with that in Fig.3-32).

LOW-PASS SECTION NEAR  $R_{\rm H}$

If the sequence of the sections is now reversed, the situation is as in Fig.3-33.

In this case, the normalized element values have to be inverted, so:

$$g_1 = k \sqrt{\frac{m}{k-1}}$$

$$g_2 = \frac{1}{\sqrt{m(k-1)}}$$

$$g_3 = \sqrt{\frac{k-1}{m}}$$

$$g_4 = \frac{1}{k} \sqrt{m(k-1)}$$

Denormalization is done as in the previous case, and the maximum VSWR remains the same  $(1/\epsilon^2)$ .

To match 2.5 to 50  $\Omega$  over 132 to 174 MHz, (see Section 3.2.2.3.2), the calculation gives the following results:

#### 1st case (circuit as in Fig.3-32):

$L_1 = 5.005 \text{ nH}$ ;  $C_2 = 167.7 \text{ pF}$

$C_3 = 52.6 \text{ pF}$ ;  $L_4 = 27.54 \text{ nH}$

### 2nd case (circuit as in Fig.3-33):

$C_1 = 220.3 \text{ pF}$ ;  $L_2 = 6.575 \text{ nH}$

$L_3 = 20.97 \text{ nH}$ ;  $C_4 = 40.04 \text{ pF}$ .

VSWR (both cases) = 1.14

## Power amplifier design

The results are slightly better than those obtained with two low-pass sections. Other advantages are:

- Easier calculation

- Useful for interstage networks.

A disadvantage is the reduced suppression of harmonics.

Effect of real ('imperfect') components on the calculations

When implementing these wideband networks, keep in mind that capacitors, even surface-mount (chip) capacitors, are not ideal components. A chip capacitor, for example, has a series inductance of about 1 nH. In the example with two low-pass sections, a capacitance of 197 pF was required. If two capacitors in parallel are used, their combined inductance is 0.5 nH. As a consequence, we have to reduce the capacitance to C' where:

$$C' = \frac{C}{\omega^2 LC + 1}$$

Note,  $\boldsymbol{\omega}$  is the average angular frequency of the band, so in the example:

$$C' = \frac{197}{1.09} = 181 \text{ pF}$$

### 3.2.2.4 THE LOWER UHF RANGE

For the lower UHF range, the methods used in the upper VHF range can again be employed. However, it is not always very practical to use discrete inductances because of the very low values required, and these should then be replaced by striplines.

Note that a stripline is not a pure series inductance; it has parallel capacitance which must be taken into account in any network design. In addition, a particular inductance can be obtained with striplines of different characteristic resistance,  $R_{\text{c}}.$  Wherever, possible, use striplines with relatively high  $R_{\text{c}}$  as they generally have lower parallel capacitances.

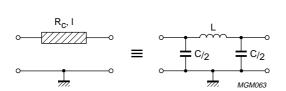

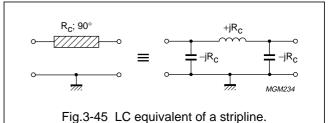

If a transmission line is shorter than 1/8th of a wavelength, a good approximation is the LC equivalent circuit shown in Fig.3-34 where:

$L = R_c I/v$

$C = I/R_c v$

where  $v = 3x10^8/\sqrt{\epsilon_r}$ . ( $\epsilon_r$  being the *effective* relative dielectric constant of the print board).

What was said about the parasitic inductance of real capacitors at VHF frequencies is of course even more relevant at UHF frequencies.

# Power amplifier design

# WIDEBAND UHF MATCHING CIRCUITS OVERVIEW

Lower UHF range (Section 3.2.2.4)

In this range, the techniques used in the upper VHF range can again be used. The main difference is the more frequent use of striplines. In Section 3.2.2.4, the equivalence between striplines and LC-networks is given.

Upper UHF range (Section 3.2.2.5)

- This section outlines the considerations for very wide bandwidths (about 1 octave).

- Section 3.2.2.5.1 covers the use of band-pass networks for the output circuit. These are based on an equivalent low-pass circuit and contain one or two Norton transformations (inductive and capacitive) including T and Pi equivalents.

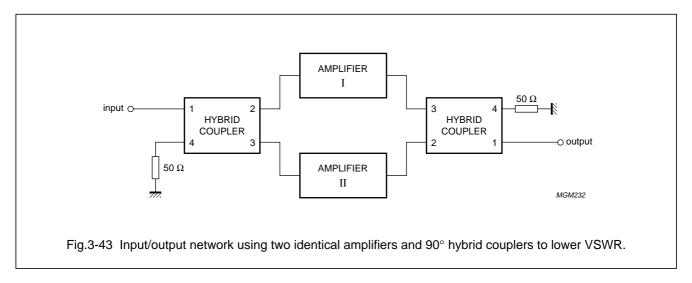

- Input networks for this range are usually designed for the highest possible flat power gain, and often have a poor input VSWR at the lower end of the range. To improve performance, two identical amplifiers can be combined with 3 dB 90° hybrid couplers as outlined in Section 3.2.2.5.2. Constructing couplers for less-demanding applications is also described, as is the design procedure for the input matching network.

Fig.3-34 LC equivalent circuit of a transmission line shorter than 1/8th of a wavelength.

### 3.2.2.5 THE UPPER UHF RANGE

Here, we shall consider wideband circuits for TV bands IV and V, covering 470 to 860 MHz, i.e. a bandwidth of 390 MHz.

In Section 3.2.2.3 (Upper VHF range), we described how to match two widely different resistances over a wide range of frequencies. For two pure resistances, matching is always possible, though more sections are required as

the resistance ratio and/or the relative bandwidth increases.

Now consider when one or both impedances have a large reactive component - a parallel-RC combination, or a series-RL circuit. In both cases, a time constant,  $\tau$ , is involved:  $\tau$  = RC or L/R.

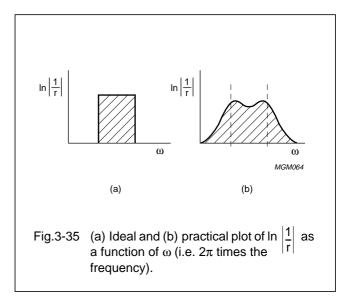

According to Bode (see also Refs 6 and 7), there is a limit to the reflection coefficient, r, which can be achieved in the pass-band. This limit depends on the time constant and the required (absolute) bandwidth, even when the number of elements in the matching network is made arbitrarily high and is:

$$\int_{0}^{\infty} \ln \left| \frac{1}{r} \right| d\omega = \frac{\pi}{\tau}$$

If we assume that r is constant in the pass-band, and equal to one in the stop-bands, this relation can be simplified to:

$$2\pi B\tau \,=\, \pi/In \, \left|\frac{1}{r}\right|$$

where B is the absolute bandwidth.

This relationship is shown in Fig.3-35.

According to Bode, the area below the curve is given by the time constant. If r is less than 1 in the stop-bands, and varies in the pass-band, then the maximum value of r in the pass-band will be higher than the theoretical value.

For example, suppose the maximum acceptable VSWR in the pass-band is 1.25, then r = 0.111. For the ideal case, this gives:  $2\pi B\tau$  = 1.43; in practice,  $2\pi B\tau$  will rarely exceed 1.0, and then only by a very small amount.

## Power amplifier design

#### 3.2.2.5.1 OUTPUT NETWORKS

As an example, take the BLW98, a class-A TV-transposer transistor for bands IV/V (bandwidth, B = 390 MHz). At  $V_{CE}$  = 25 V and  $I_{C}$  = 0.85 A, a BLW98 is able to deliver about 4 W peak sync power with a 3-tone intermodulation distortion of –60 dB. Under these conditions, the effective output capacitance,  $C_{C}$ , is ~20 pF, and the optimum load resistance in class-A operation is ~20  $\Omega$ . So the time constant,  $\tau$ , of the transistor output is ~400 ps, and  $2\pi B\tau$  then becomes 0.98, meaning that the required bandwidth can just be realized without serious concessions in output power and IMD in parts of the frequency band.

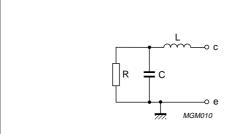

The equivalent output circuit of a transistor without internal output matching is shown in Fig.3-36.

Fig.3-36 Equivalent circuit of the output of a transistor without internal output matching.

The values of R, C and L can be derived from the published curves for optimum load impedance versus frequency. Here, computer programs for circuit analysis with an optimization facility can be very helpful. A good approximation however can also be made using the following:

- R: In class-A amplifiers, R =  $NV_{CE}/I_C$  where N = 0.65 to 0.80. In other classes, R =  $V_C^2/(2P_o)$  but note that for linear class-AB amplifiers,  $V_C$  must be chosen 10 to 15% below the supply voltage.

- C: In the HF and VHF range,  $C = NC_C$  where N = 1.10 to 1.15. In the UHF range (especially in the upper part), higher efficiency and gain can be obtained when the output capacitance is not completely tuned out. In practice, an amount  $\Delta C = 0.5/(\omega_m R)$  may be subtracted where  $\omega_m$  is the maximum angular frequency of the band.

- L: This is approximately  $L_c + L_e/2$  (about 1 to 2 nH in practice) where  $L_c$  and  $L_e$  are respectively the collector and emitter self-inductance.

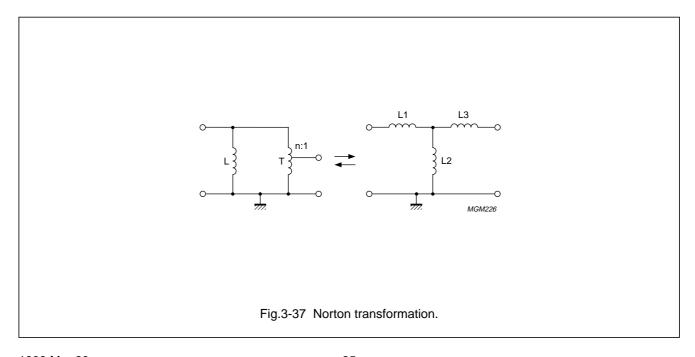

The next step is to choose the configuration of the matching network. Where a large bandwidth is required, as in this example, it can be a big advantage to make the collector RF choke part of the matching network. This can be arranged in two ways. The simplest is where the collector RF choke tunes out the imaginary part of the output impedance in the middle of the band. A better and theoretically more correct method is to apply a Norton transformation as shown in Fig.3-37.

# Power amplifier design

T is an ideal transformer which transforms the voltage down by a factor n (n > 1). 'Ideal' means the transformer has no parallel and no stray inductance, i.e. there is 100% coupling between the windings.

The other quantities are:

$$L_1 = L\left(1 - \frac{1}{n}\right)$$

$$L_2 = \frac{L}{n}$$

$$L_3 = \frac{-L(n-1)}{n^2}$$

Note,  $L_3$  is negative but this is subsequently 'absorbed' in the remainder of the network.  $L_1 \ge L$  in the equivalent output circuit (Fig.3-36) of the transistor.

Combining Figs 3-36 and 3-37 yields Fig.3-38. So, the transistor output impedance becomes a parallel connection of R', C' and L' where:

$$R' = \frac{R}{n^2}$$

$C' = Cn^2$

$$L' = \frac{L}{n^2}$$

Now we can arrange that the LC-parallel circuit resonates in the middle of the frequency band. Furthermore, we can vary R' within certain limits.

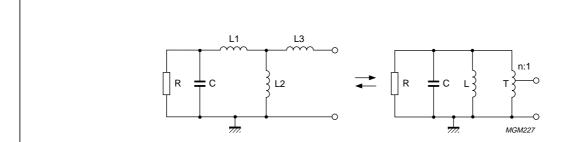

At the 50  $\Omega$  side, the same kind of transformation in reverse can be made if required. In this case, a capacitive transformation is also possible, see Fig.3-39 where:

$$C_1 = \frac{-n^2C}{n-1}$$

$$C_2 = nC$$

$$C_3 = \frac{nC}{n-1}$$

Here,  $C_1$  is negative and so it has also to be absorbed in the remainder of the network.

Fig.3-38 Norton transformation at transistor output.

Fig.3-39 Alternative transformation at 50  $\Omega$  load side.

# Power amplifier design

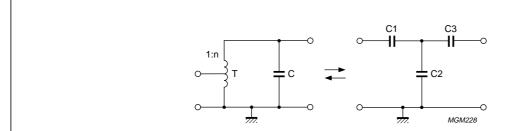

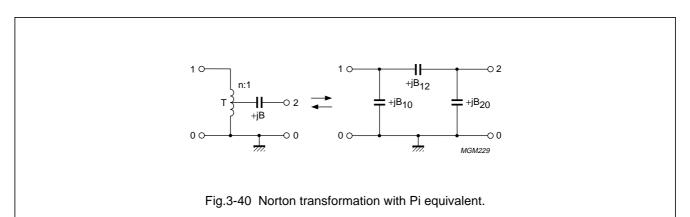

Sometimes a Pi-equivalent is needed instead of a T-equivalent. This can be obtained as indicated in Fig.3-40 for the capacitive case where:

$$B_{12} = \frac{B}{n}$$

$$B_{20} = B\left(1 - \frac{1}{n}\right)$$

$$B_{10} = \frac{-B(n-1)}{n^2}$$

This transformation also has an inductive equivalent in which B =  $-1/\omega L$  instead of  $\omega C$ .

Now we return to Fig.3-38 to complete the impedance matching. Several methods are possible:

- The Matthaei method as described in Section 3.2.2.3.2

- The Fleischmann method as described in Section 3.2.2.3.2

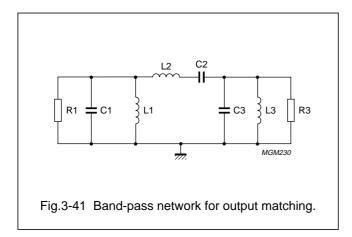

- A band-pass network as depicted in Fig.3-41.

The network of Fig.3-41 can only be used if  $R_1$  does not differ too much from  $R_3$ , say  $2R_3 \ge R_1 \ge R_3/2$ . If so, we can apply the Norton transformation (just discussed) at the input and, if necessary, also at the output.

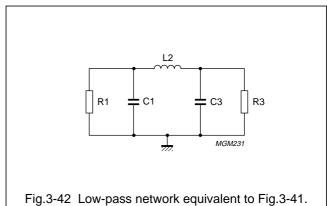

This band-pass network has been derived from an equivalent low-pass Chebyshev filter as shown in Fig.3-42.

Components with the same identifiers (in Figs 3-41 and 3-42) have the same values. Components  $L_1$ ,  $C_2$  and  $L_3$ , added in the band-pass network, resonate with the parallel or series-connected components at the geometric mean frequency of the passband,  $f_0$ :

$$f_0 = \sqrt{f_1 f_2}$$

where  $f_1$  and  $f_2$  are the lower and upper limits of the pass-band respectively.

$\mathsf{L}_1$  resonates with  $\mathsf{C}_1;\,\mathsf{C}_2$  resonates with  $\mathsf{L}_2,$  and  $\mathsf{L}_3$  resonates with  $\mathsf{C}_3$

In Fig.3-42, without a Norton transformation:

$$R_1 = R_3$$

$$C_1 = C_3$$

.

# Power amplifier design

By combining some equations from the two-element compensation of Section 3.2.2.1.1, we can express  $L_2$  as:

$$L_{2} = \frac{8R_{1}^{2}C_{1}}{3(\omega C_{1}R_{1})^{2} + 4}$$

where  $\omega$  is  $2\pi$  times the required bandwidth. The maximum VSWR of this network can be calculated in the same way as in Section 3.2.2.1.1 where:

$$\gamma = \frac{1}{\omega R_1 C_1}$$

and

$$k = \gamma + \sqrt{\gamma^2 + 1}$$

from which

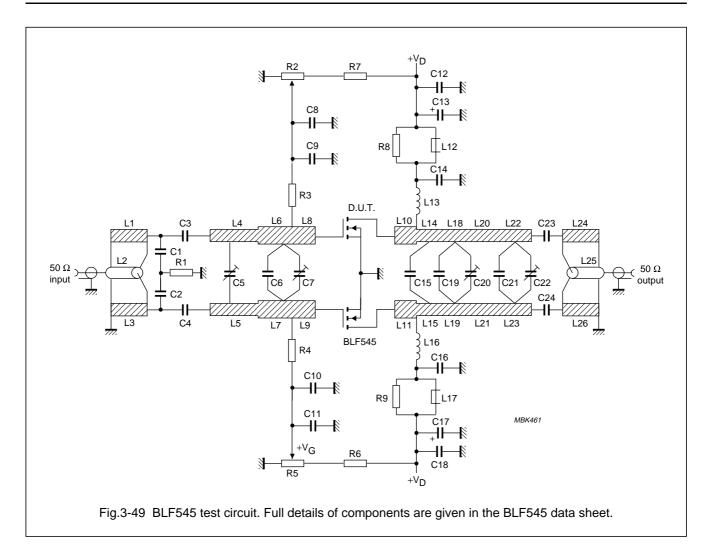

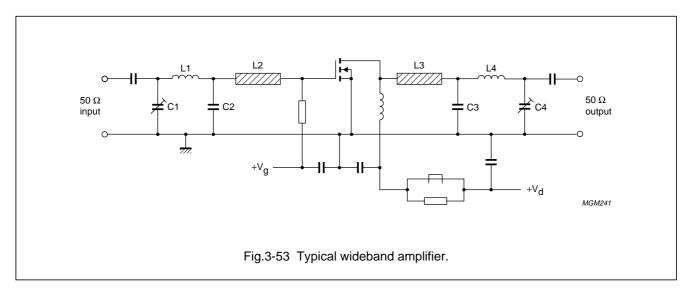

$$VSWR = \left(\frac{k^3 + 1}{k^3 - 1}\right)^2$$